机密★启用前

2024 年 10 月高等教育自学考试全国统一考试

微型计算机原理及其应用

(课程代码 02351)

注意事项

1.本试卷分为两部分,第一部分为选择题,第二部分为非选择题。

2.应考者必须按试题顺序在答题卡 (纸) 指定位置上作答,答在试卷上无效。

3.涂写部分、画图部分必须使用 2B 铅笔,书写部分必须使用黑色字迹签字笔。

第一部分 选择题

一、单项选择题:本大题共 20 小题,每小题 1 分,共 20 分。在每小题列出的备选项中只有一项是最符合题目要求的,请将其选出。

1. 8086CPU 引脚可以传送多少位地址( )

A. 8 B. 16 C. 20 D. 24

2.8086CPU 标志寄存器中进位标志位是( )

A. DF B. IF C. CF D. TF

3.以下选项属于计算机软件的是( )

A. 存储器 B. 鼠标 C. 显示器 D. office 工具

4.RAM 的特点是( )

A. 只能读出数据 B. 断电后信息丢失 C. 只能写入数据 D. 不能读也不能写

5.在 8086 系统中,设指令 MOV AX, [1023H] 已经在指令队列中并准备执行,则执行此指令需要总线周期数为( )

A. 1 个 B. 2 个 C. 3 个 D. 4 个

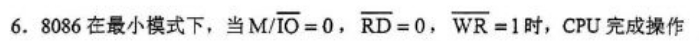

A. 存储器读 B. I/O 读 C. 存储器写 D. I/O 写

7.以下哪个芯片能实现串行通信( )

A. 8255A B. 8251A C. 8259A D. 8253 – 5

8.对于 8255A 的 OBF 信号,下列描述中,正确的是( )

A. 外设送给 8255A 的信号 B. 输入缓冲器满信号 C. CPU 送给 8255A 的信号 D. 输出缓冲器满信号

9. 7 片 8259 级联可连接多少个中断源( )

A. 22 B. 23 C. 24 D. 25

10.8086/8088 的中断向量表是( )

A. 用于存放子程序的返回地址 B. 用于存放中断服务程序的入口地址 C. 用于存放中断服务程序的返回地址 D. 用于存放子程序的入口地址

11. 8253 – 5 总共有几个独立的 16 位计数器( )

A. 3 B. 4 C. 5 D. 6

12.十进制数 23 的 8421BCD 码是( )

A. 20 B. 22 C. 23 D. 32

13. DAC0832 是一种常用的( )

A. 模 / 数转换器芯片 B. 数 / 模转换器芯片 C. 微处理器芯片 D. 并行转换器芯片

14.可屏蔽中断请求信号是从以下哪个引脚送入 CPU( )

A. INTR B. READY C. RESET D. CLK

15.8086 处理器有多少根数据线( )

A. 8 B. 16 C. 20 D. 24

16. 8088/8086 中,紧跟 T₁之后可能出现的状态是( )

17. 8086 最多能处理的中断类型有多少种( )

A. 253 B. 254 C. 255 D. 256

18.以下关于周期时间长短的说法中正确的是( )

A. 总周期 < 时钟周期 < 指令周期 B. 时钟周期 < 总周期 < 指令周期 C. 指令周期 < 总线周期 < 时钟周期 D. 时钟周期 < 指令周期 < 总周期

19.有一半导体存储芯片,其 MAR 为 11 位,存储字长为 8 位,该芯片的容量是( )

A. 1K×8 位 B. 2K×8 位 C. 2K×16 位 D. 1K×16 位

20.以下哪种传送方式要求在执行输入操作时,外设一定是 “准备好” 状态( )

A. 无条件传送 B. 中断传送 C. 查询传送 D. DMA

二、判断题

本大题共 10 小题,每小题 1 分,共 10 分。判断下列各题正误,正确的在答题卡相应位置涂 “A”,错误的涂 “B”。

21. 外设接口电路同外设之间交换的控制信息是通过 CPU 的控制总线传送的。

22. 控制器就是中央处理机,简称 CPU。

23. 8259A 只有两个端口地址。

24. 8253 – 5 的计数器中的计数初值寄存用来完成减 1 计数操作。

25. 存储器寻址的指令,其操作数在存储器中。

26. 微机中地址总线的作用是用于选择存储器单元。

27. 8259A 的自动循环方式是一种中断源的中断优先级别将随着中断响应过程的结束而随时跟着变化的中断优先权管理方式。

28. 问号不能单独作为标识符。

29. 宏定义的命令是 SEGMENT。

30. 部分译码法对应存储器芯片中任意单元都有唯一确定的地址。

第二部分 非选择题

三、填空题:本大题共 15 小题,每小题 1 分,共 15 分。

31. 内存容量中的最大容量由 CPU 的______的位数决定。

32. 8088 的指令队列是______字节长。

33. IP 指向的是指令地址的段内______地址。

34. 计算机能执行的指令必须以______进制代码的形式表示。

35. 指令 MOV AX, 12 中源操作数的寻址方式是______寻址。

36. 启动两次独立的存储器操作之间所需的最小时间间隔称为存储器的______。

37. 8086 存储体系中的偶存储体容量是______字节。

38. I/O 端口的编址方式有两种:编址和存储器映像编址。

39. 接口中可以由 CPU 进行读或写的寄存器称为。

40. 8255A 的 A 组控制部件用来控制 PA 口和 PC 口的______。

41. 8253 – 5 设定为方式 1 工作时,输出 OUT 变为______电平。

42. RS – 232C 属于外总线,又称为______总线。

43. USB 的主要规范中,最多可连接______个外设装置(包括转换器 – HUB)。

44. JNZ 跳转满足的条件是 ZF =______。

45. AL = 0000 0001B,执行指令 OR AL, 0000 1111B 以后,AL =______B。

四、名词解释题:本大题共 4 小题,每小题 5 分,共 20 分。

46. 逻辑地址

47. 指令的机器码

48. “对准的” 字

49. 中断

五、简答题:本大题共 3 小题,每小题 5 分,共 15 分。

51. 简述 PC/XT 系统板上各部件同三种总线(芯片总线、系统总线、系统扩充总线)之间的关系。

52. 简述 DRAM 的特点。

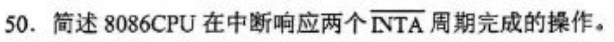

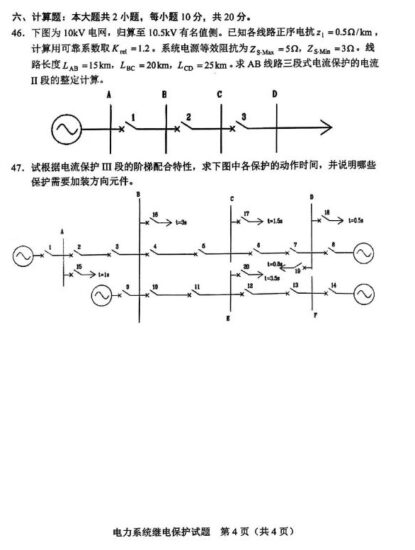

六、综合应用题:本大题共 2 小题,每小题 10 分,共 20 分。

53. 已知 8253 – 5 的端口地址:计数器 0 端口地址 20H,计数器 1 端口地址 21H,计数器 2 端口地址 22H,控制字寄存器端口地址 23H,完成 8253 – 5 的初始化,要求:计数器 2 工作于方式 0,计数初值为 (1234)₁₀,BCD 计数,8253 控制字为 10010001B。

MOV AL,①______B

OUT ②______H, AL

MOV AL, 34H

OUT ③______H, AL

MOV AL, ④______

OUT ⑤______H, AL

54. 已知 8255A 端口地址为 80H、81H、82H、83H,要求端口 A 工作于方式 1 输入,端口 B 工作于方式 1 输出,要求完成对 8255A 芯片的初始化,对 PC₀置 1,通过端口 B 输出数据 10H,方式选择控制字为 10110100B,置位复位控制字为 00000001B。

MOV AL,①______B

OUT ②______H, AL

MOV AL, ③______B

OUT ④______H, AL

MOV AL, 10H

OUT ⑤______H, AL

2024 年 10 月高等教育自学考试全国统一命题考试

02351 微型计算机原理及其应用 参考答案

一、单项选择题:本大题共 20 小题,每小题1分,共 20 分,

1.C 2.C 3.D 4.B 5.B

6.B 7.B 8.D 9.A 10.B

45.0000 1111

四、名词解释题:本大题共 4 小题,每小题5 分,共 20 分。

46.逻辑地址

逻辑地址是 8086 微处理器中由段地址和偏移地址组成的地址形式。程序通过逻辑地址访问内存,物理地址通过公式 段地址 x 16 + 偏移地址 计算得到。例如,段地址为 2000H,偏移地址为 0300H 时,物理地址为 20300H。逻辑地址使得程序可以灵活管理内存,独立于物理存储布局。

47.指令的机器码

指令的机器码是计算机能够直接识别和执行的二进制编码形式。每条汇编指令对应唯一的机器码,例如指令`MOV AX,12H`的机器码为B8 12 00`。机器码由操作码(操作类型)和操作数(数据或地址)组成,是CPU执行指令的基础。

48.“对准的”字

在 8086 系统中,“对准的字”指存储于偶地址的 16 位数据(如地址2000H)。访问对准的字时,CPU仅需一个总线周期即可完成读写操作;若字存储于奇地址(如 2001H),则需两个总线周期,称为未对齐访问。对齐访问可提升系统性能,减少总线操作时间。

49.中断

中断是 CPU 暂停当前任务,转去执行特定服务程序的过程。中断可由硬件(如外设请求)或软件(如INT指令)触发。中断响应时,CPU 通过中断类型号查询中断向量表,获取中断服务程序的入口地址,执行完毕后返回原任务。中断机制提高了系统的实时性和多任务处理能力。

五、简答题:本大题共 3 小题,每小题 5 分,共 15 分。

50.第一个总线周期:发送中断响应信号(INTA),获取中断类型号。第二个总线周期:读取中断类型号,并跳转到中断向量 表对应入口地址。

51.芯片总线:连接 CPU 与主板上的核心芯片(如时钟发生器、中断控制器 8259A、DMA 控制器 8237 等),用于高速、低延迟的局部通信。

系统总线:主板上的主总线(如地址总线、数据总线、控制总线),连接 CPU、内存(DRAM)、主 I/O 接口(如 8255A、8253)等核心部件,负责全局数据传输。

系统扩充总线:通过扩展插槽(如ISA 总线)连接外部设备(如显卡、硬盘控制器)为系统提供扩展能力。

关系总结:芯片总线服务于 CPU 与邻近芯片的交互:系统总线整合核心部件通信:系统扩充总线扩展外设功能,三者协同实现系统功能分层与扩展。

52.需要定期刷新:存储单元基于电容电荷,电荷会逐渐泄漏,需周期性刷新(通常由内存控制器管理)以维持数据。

高集成度、低成本:结构简单,单个存储单元仅需一个晶体管和一个电容,适合大规模集成,单位容量成本低。

速度较 SRAM 慢:因刷新机制和电容充放电特性,存取速度低于静态 RAM(SRAN),但容量更大。

用于主内存:凭借高密度和低成本优势,广泛应用于计算机主存储器(如内存条)。功耗较低:相比 SRAM,动态刷新虽增加功耗,但整体仍更节能。

六、综合应用题:本大题共 2 小题,每小题 10 分,共 20 分。

53.8253-5 初始化代码:

MOV AL, 10010001B

OUT 23H, AL

MOV AL, 34H

OUT 22H, AL

MOV AL, 12H

OUT 22H, AL

54.8255A初始化代码:

MOV AL, 10110100B

OUT 83H, AL

MOV AL, 00000001B

OUT 83H, AL

MOV AL, 10H

OUT 81H, AL

(注:①填 10110100,②填 83,③填 00000001,④填 83,⑤填 81)

(答案仅供参考,以官版评分标准为准。)

(2)本站自学考试信息供自考生参考,权威信息以各省(市)考试院官方为准。

暂无评论内容